近日,“英特爾精尖制造日”活動在京舉行。英特爾公司執(zhí)行副總裁,制造、運(yùn)營與銷售集團(tuán)總裁Stacy Smith否定了業(yè)界傳出的“摩爾定律失效”的說法,并且首次在中國展示英特爾首款10納米FPGA的計(jì)劃,并宣布了業(yè)內(nèi)首款面向數(shù)據(jù)中心應(yīng)用的64層3D NAND產(chǎn)品已實(shí)現(xiàn)商用并出貨。

圖:英特爾公司執(zhí)行副總裁,制造、運(yùn)營與銷售集團(tuán)總裁Stacy Smith

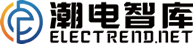

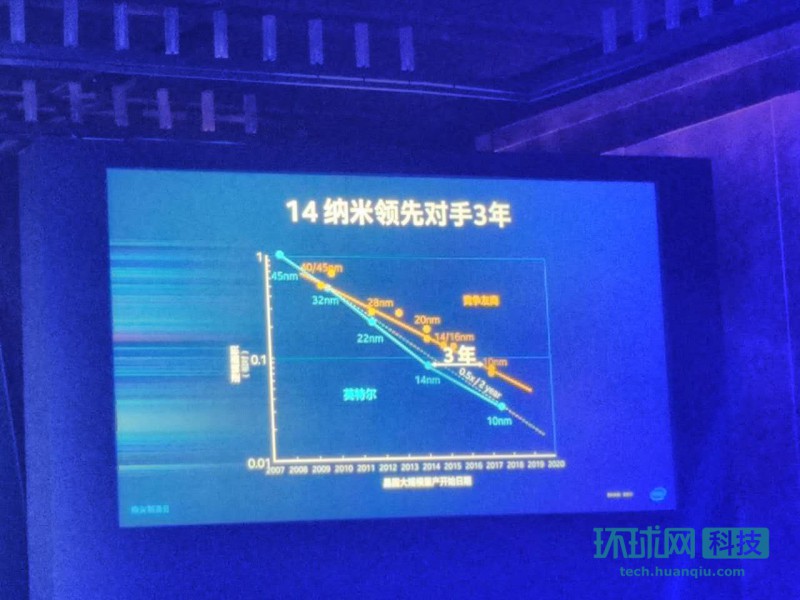

“英特爾一直以來都是,并將繼續(xù)成為推動摩爾定律向前發(fā)展的技術(shù)領(lǐng)導(dǎo)者,目前英特爾在制程工藝上保持著大約三年的領(lǐng)先性。”Stacy Smith進(jìn)表示,英特爾推動摩爾定律不斷向前發(fā)展,每一年都持續(xù)降低產(chǎn)品價(jià)格并提升其性能,這也是英特爾的核心競爭優(yōu)勢所在。

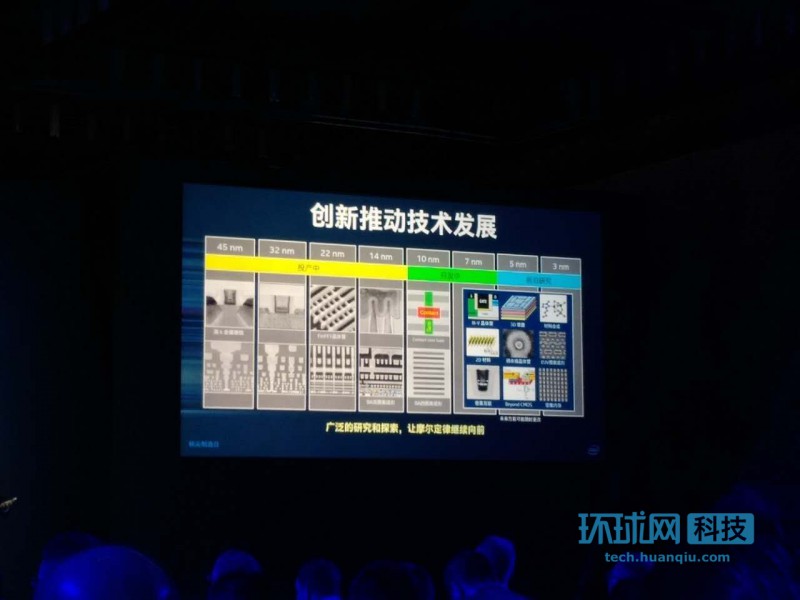

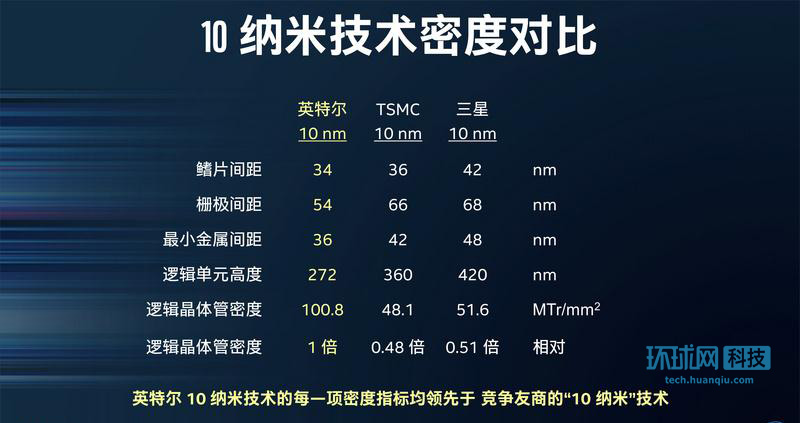

他提到,正是超微縮技術(shù)(hyper scaling)讓英特爾能夠加速推進(jìn)密度的提升,借助節(jié)點(diǎn)內(nèi)優(yōu)化,產(chǎn)品功能每年都可以實(shí)現(xiàn)增強(qiáng)。據(jù)悉,英特爾10納米制程工藝擁有世界上最密集的晶體管和最小的金屬間距,從而實(shí)現(xiàn)了業(yè)內(nèi)最高的晶體管密度。

Stacy Smith指出,英特爾10納米制程的最小柵極間距從70納米縮小至54納米,且最小金屬間距從52納米縮小至36納米。尺寸的縮小使得邏輯晶體管密度可達(dá)到每平方毫米1.008億個(gè)晶體管,是之前英特爾14納米制程的2.7倍,大約是業(yè)界其他“10納米”制程的2倍。

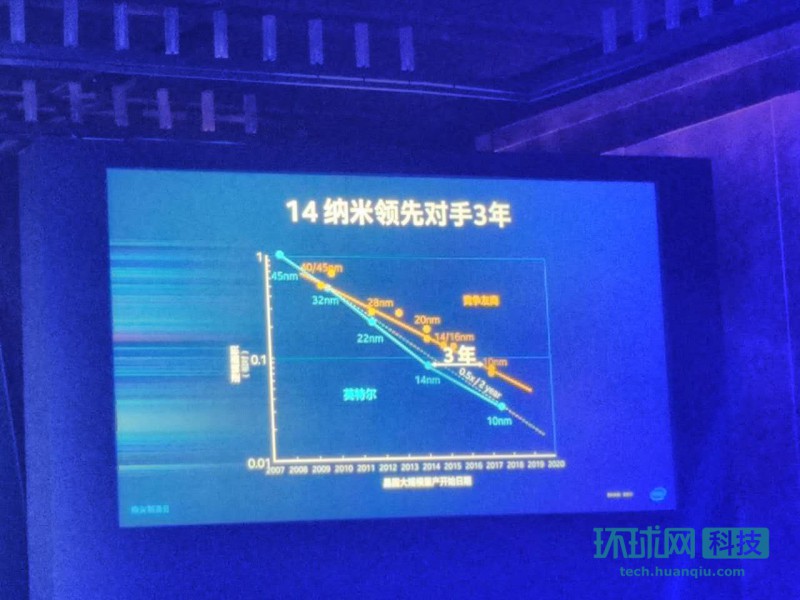

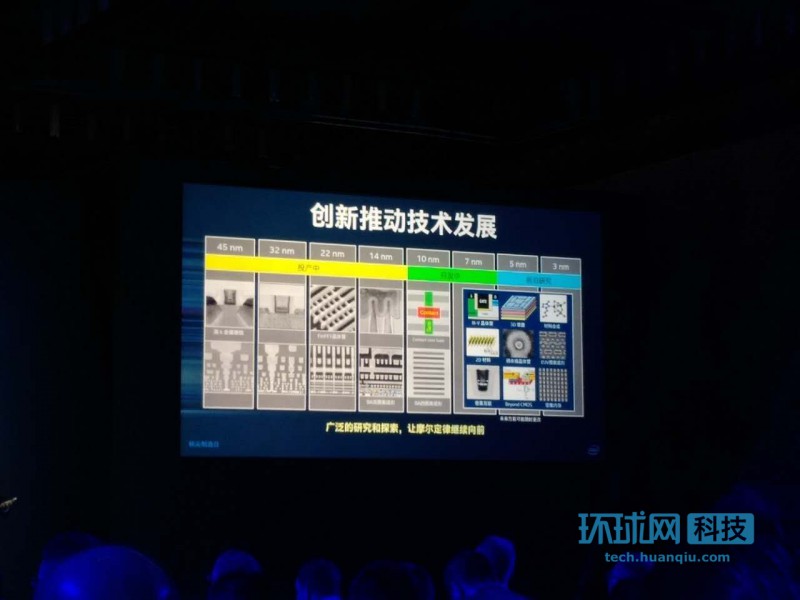

對于業(yè)界探討的“摩爾定律是否失效”的問題,Stacy Smith堅(jiān)定的認(rèn)為不會。“每一個(gè)節(jié)點(diǎn)晶體管數(shù)量會增加一倍,14nm和10nm都做到了,而且晶體管成本下降幅度前所未有,這表示摩爾定律仍然有效。”Stacy Smith解釋道,“創(chuàng)新技術(shù),可以保證摩爾定律長期有效。”

另外,現(xiàn)場還展出了經(jīng)過展訊驗(yàn)證的英特爾晶圓代工業(yè)務(wù)14 納米平臺。英特爾14納米制程采用第二代FinFET 技術(shù),提升性能并降低漏電功耗。

英特爾高級院士馬博(Mark Bohr)介紹了英特爾22FFL功耗和性能的最新細(xì)節(jié)。22FFL是在2017年3月美國“英特爾精尖制造日”活動上首次宣布的一種面向移動應(yīng)用的超低功耗FinFET技術(shù)。英特爾22FFL可帶來一流的CPU性能,實(shí)現(xiàn)超過2GHz的主頻以及漏電降低100倍以上的超低功耗。此外,22FFL晶圓在本次活動上全球首次公開亮相。

據(jù)悉,與先前的22GP(通用)技術(shù)相比,全新22FFL技術(shù)的漏電量最多可減少100倍。22FFL工藝還可達(dá)到與英特爾14納米晶體管相同的驅(qū)動電流,同時(shí)實(shí)現(xiàn)比業(yè)界28納米/22納米平面技術(shù)更高的面積微縮。22FFL工藝包含一個(gè)完整的射頻(RF)套件,并結(jié)合多種先進(jìn)的模擬和射頻器件來支持高度集成的產(chǎn)品。

2017年6月,高通總裁里克·阿伯利曾表示,之前的處理器龍頭Intel在10nm制程技術(shù)明顯落后;高通方面也曾表示,驍龍835處理器采用的是三星10nm芯片制造技術(shù),這意味著其移動芯片超過了個(gè)人計(jì)算機(jī)處理器。

在業(yè)內(nèi)人士看來,一向低調(diào)的英特爾在活動當(dāng)天不斷提到友商的問題;從來不跟友商比較的英特爾還明確地跟三星和TSMC在10納米技術(shù)上做對比。尤其在媒體采訪環(huán)節(jié),英特爾中國區(qū)總裁楊旭提到了制程節(jié)點(diǎn)命名的混亂,認(rèn)為制程技術(shù)應(yīng)該以實(shí)踐進(jìn)行度量;在媒體的追問下,他給出強(qiáng)勢回應(yīng)“老虎不說話(發(fā)威),當(dāng)我們病貓呢”。

最后,Stacy Smith認(rèn)為,“我們在14nm上與競爭對手相比領(lǐng)先3年??梢钥吹接焉叹w管密度并沒有提升,友商10nm節(jié)點(diǎn)晶體管密度只相當(dāng)于我們14nmd的晶體管密度。”